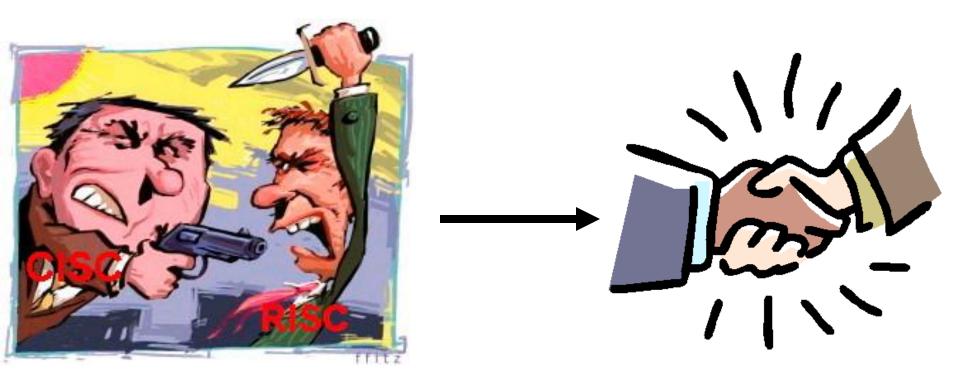

## RISC Vs CISC

- CISC (complex instruction set computer)

- VAX, Intel X86, IBM 360/370, etc.

- RISC (reduced instruction set computer)

- MIPS, DEC Alpha, SUN Sparc, IBM 801

# RISC vs. CISC

## Characteristics of ISAs

| CISC               | RISC         |

|--------------------|--------------|

| Variable length    | Single word  |

| instruction        | instruction  |

| Variable format    | Fixed-field  |

|                    | decoding     |

| Memory operands    | Load/store   |

|                    | architecture |

| Complex operations | Simple       |

|                    | operations   |

# RISC vs. CISC Instruction Set Design

- The historical background:

- In first 25 years (1945-70) performance came from both technology and design.

- Design considerations:

- small and slow memories: compact programs are fast.

- small no. of registers: memory operands.

- attempts to bridge the semantic gap: model high level language features in instructions.

- no need for portability: same vendor application, OS and hardware.

- backward compatibility: every new ISA must carry the good and bad of all past ones.

Result: powerful and complex instructions that are rarely used.

# Top 10 80x86 Instructions

| ° Rank | instruction       | nteger Average Percent total executed |

|--------|-------------------|---------------------------------------|

| 1      | load              | 22%                                   |

| 2      | conditional brand | ch 20%                                |

| 3      | compare           | 16%                                   |

| 4      | store             | 12%                                   |

| 5      | add               | 8%                                    |

| 6      | and               | 6%                                    |

| 7      | sub               | 5%                                    |

| 8      | move register-reg | gister 4%                             |

| 9      | call              | 1%                                    |

| 10     | return            | 1%                                    |

|        | Total             | 96%                                   |

Simple instructions dominate instruction frequency

## Complex Instruction Set Computer (CISC)

Memory in those days was expensive

bigger program->more storage->more money

Hence needed to reduce the number of instructions per program

Number of instructions are reduced by having multiple operations within a single instruction

Multiple operations lead to many different kinds of instructions that access memory

- In turn making instruction length variable and fetch-decodeexecute time unpredictable – making it more complex

- Thus hardware handles the complexity

Example: x86 ISA

## Reduced Instruction Set Computer (RISC)

## Original idea to reduce the ISA

Provide minimal set of instructions that could carry out all essential operations

Instruction complexity is reduced by

- Having few simple instructions that are the same length

- Allowed memory access only with explicit load and store instructions

Hence each instruction performs less work but instruction execution time among different instructions is consistent

The complexity that is removed from ISA is moved into the domain of the assembly programmer/compiler

Examples: LC3, MIPS, PowerPC (IBM), SPARC (Sun)

## RISC vs. CISC

The difference between CISC and RISC becomes evident through the basic computer performance equation:

$$\texttt{CPU Time} = \frac{\texttt{seconds}}{\texttt{program}} = \frac{\texttt{instructions}}{\texttt{program}} \times \frac{\texttt{avg. cycles}}{\texttt{instruction}} \times \frac{\texttt{seconds}}{\texttt{cycle}}$$

RISC systems shorten execution time by reducing the *clock* cycles per instruction (i.e. simple instructions take less time to interpret)

CISC systems shorten execution time by reducing the number of instructions per program

## Example for RISC vs. CISC

Consider the the program fragments:

The total clock cycles for the CISC version might be:

$(2 \text{ movs} \times 1 \text{ cycle}) + (1 \text{ mul} \times 30 \text{ cycles}) = 32 \text{ cycles}$

While the clock cycles for the RISC version is:

(3 movs × 1 cycle) + (5 adds × 1 cycle) + (5 loops × 1 cycle) = 13 cycles

## RISC vs. CISC Summary

### RISC

- Simple instructions, few in number

- Fixed length instructions

- Complexity in compiler

- Only LOAD/STORE instructions access memory

- · Few addressing modes

### CISC

- Many complex instructions

- Variable length instructions

- Complexity in microcode

- Many instructions can access memory

- Many addressing modes

#### CISC

Emphasis on hardware

Includes multi-clock complex instructions

Memory-to-memory:

"LOAD" and "STORE"

incorporated in instructions

Small code sizes, high cycles per second

#### **RISC**

Emphasis on software

Single-clock, reduced instruction only

Register to register:

"LOAD" and "STORE"

are independent instructions

Low cycles per second, large code sizes

# **Comparison of Processors**

|                                         | Complex Instruction Set<br>(CISC)Computer |               |                | Reduced Instruction<br>Set (RISC) Computer |               | Superscalar |                |                |

|-----------------------------------------|-------------------------------------------|---------------|----------------|--------------------------------------------|---------------|-------------|----------------|----------------|

| Characteristic                          | IBM<br>370/168                            | VAX<br>11/780 | Intel<br>80486 | SPARC                                      | MIPS<br>R4000 | PowerPC     | Ultra<br>SPARC | MIPS<br>R10000 |

| Year developed                          | 1973                                      | 1978          | 1989           | 1987                                       | 1991          | 1993        | 1996           | 1996           |

| Number of instructions                  | 208                                       | 303           | 235            | 69                                         | 94            | 225         |                |                |

| Instruction size (bytes)                | 2–6                                       | 2–57          | 1–11           | 4                                          | 4             | 4           | 4              | 4              |

| Addressing modes                        | 4                                         | 22            | 11             | 1                                          | 1             | 2           | 1              | 1              |

| Number of general-<br>purpose registers | 16                                        | 16            | 8              | 40 - 520                                   | 32            | 32          | 40 - 520       | 32             |

| Control memory size<br>(Kbits)          | 420                                       | 480           | 246            | _                                          | _             | _           | _              | _              |

| Cache size (KBytes)                     | 64                                        | 64            | 8              | 32                                         | 128           | 16-32       | 32             | 64             |